中断8259

1.解释概念:中断,可屏蔽中断,非屏蔽中断,中断类型号,中断向量,中断向量表,

中断:处理器暂停执行当前程序,转处理随机发生事件,后返回到断点处继续执行原来程序

中断优先级依次降低:

内部中断和异常

软件中断

外部非屏蔽中断

外部可屏蔽中断

单步中断

外部中断: (CPU通过8259A芯片管理外部中断)

通过CPU的INTR管脚申请的中断请求,如:键盘中断、打印机中断、定时器中断等,是可屏蔽中断。

通过CPU的NMI管脚申请的中断请求,是不可屏蔽中断。

内部中断:

内部硬件中断:由某些特殊指令触发的中断,如单步中断、除法出错中断、溢出中断

软件中断:由指令INT n引起的非屏蔽中断,如DOS中断、BIOS中断和其他自由中断

中断响应信号输出:输出$\overline{INTA}$

中断类型码: 中断系统可处理256个中断类型(0H~0FFH号中断),每种中断安排了1字节中断类型码,每种类型的中断都有相应的中断处理程序

中断类型号乘以4就得到对应中断向量的地址 eg.21H×4=84H

中断向量表: 中断类型码对应4个字节的中断服务程序入口地址, 系统所有中断服务程序的入口地址

8086中断向量组成的中断向量表位于内存的0~3FFH区域 (4*256B)

中断向量:中断处理子程序的入口地址IP,CS

2.CPU在何时检测有无中断请求,中断响应过程是什么?

(每条指令执行的最后一个时钟周期检测中断请求)

出现以下之一,进入中断响应周期:

有软件中断;有NMI中断信号;有INTR中断信号,而且CPU允许中断响应,即IF=1

进入中断响应周期以后:

若是INTR,则产生INTA信号,中断源通过数据总线的低8位将中断类型码传送给CPU;

若是NMI,则类型码是2;

若程序出错产生中断,则使用默认的类型码;

若是中断指令,则指令中有类型码

3.如何保护原有的中断向量?如向设置新的中断向量?

保护断点:

系统自动将标志寄存器FLAG压入堆栈

清除TF和IF

将断点处的CS和IP压入堆栈,先压CS后压IP

设置新的中断向量:

系统根据中断类型码形成中断服务程序的入口地址。

转入中断服务程序执行

4.什么叫中断嵌套?何谓普通全嵌套?何谓特殊全嵌套?

一系列压栈指令进一步保护中断现场,即保护CPU各寄存器的值;

[一般应设置中断允许标志IF开放中断,以允许高级别中断请求进入;]

中断处理具体内容;

恢复现场,通过弹出堆栈指令恢复各寄存器值;

中断返回

普通EOI方式

用于全嵌套方式;8259A每得到一次EOI命令,将把当前中断服务寄存器ISR中最高的非零位清零

中断嵌套:

有优先级更高的中断源发出请求,CPU将中止正在执行的中断服务程序而转入为新的中断源服务,等新的中断服务程序执行完后,再返回到被中止的中断服务程序

普通全嵌套:

中断优先级为0~7,0级中断优先级最高;

中断类型码放到数据总线上,ISR中相应位置位并保持,直到被自动清除或被指令清除;

新收到的中断和当前ISR中的位进行比较,判断是否进行中断嵌套;可响应更高级中断请求,屏蔽同级或低级中断

特殊全嵌套: (8259级连系统中,设置主片工作于特殊全嵌套方式,从片工作于其它方式)

区别是有同级中断请求,也给予响应

8259A 功能

CPU响应中断时,为CPU提供中断类型码;

一片Intel 8259可管理8个中断请求,并把当前优先级最高的中断请求送到CPU的INTR端;

8个外部中断的优先级排列方式,可以通过对8259编程进行指定。也可以通过编程屏蔽某些中断请求;

允许9片8259级联,构成64级中断系统

中断处理程序

eg. 修改中断处理程序,需按下面的操作过程来完成:

- 读取指定中断’s 中断处理程序入口地址==>保存存储单元;

- 用户编写的程序段设置==>中断的新处理程序;

在用户程序结束之前(或不需要新的处理程序时),

把步骤1保存的入口地址恢复==>处理该中断的入口地址

1 | INTNO EQU 40H ;将占用的中断号 |

eg. 同上,user 程序使show “the bell is ringing!”

1 | DATA SEGMENT |

8259初始化、操作命令

8259A内部寄存器的选择依靠CS#、地址线A0、命令字特征位D4来选择不同的寄存器。

初始化、操作命令in两个不同的阶段

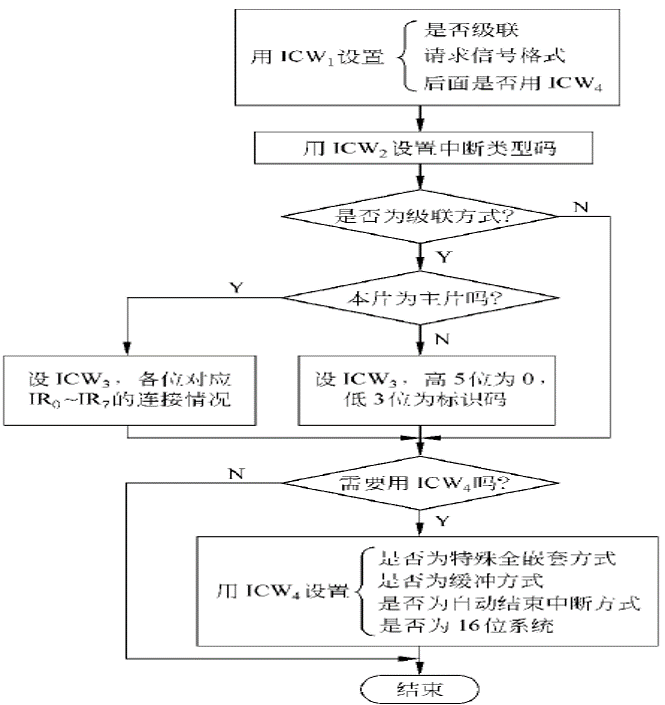

8259A初始化命令

- 对于8259A初始化一旦开始,就必须根据初始化要求,严格按流程逐一写入初始化命令

ICW1 [A0=0]

A0=0,D4=1 表示对ICW1编程;

D0(IC4)D0=1需要ICW4;D0=0 不需要ICW4;

D1(SNGL)D1=1为单片8259工作方式;D1=0 为级联工作方式,此时要用ICW3指明级联端;

D2(ADI)指明8080/8085系统中地址间距,8086系统不用(==0);

D3(LTIM)D3=1 中断请求是电平触发方式;D3=0 上升沿触发方式

eg. (8086=>D2=0)设ICW1=>D4=1,边沿触发=>D3=0,单片=>D1=0; D4~D0==10011=13H

ICW2 [A0=1]

中断类型码高5位来自ICW2高5位,低3位D2D1D0=i对应IR0~IR7的IR_{i}

ICW3 [A0=1]

包含多片8259时,ICW3才有意义<=>当SNGL=0时,才设置ICW3

本片为主片时,对ICW3相应位置Di==1表示IR0~ IR7的IR_{i}连有从片;

本片为从片时,ICW3低3位D2D1D0=i对应连接==>主片IR0~IR7的IR_{i}中断输入引脚

ICW4 [A0=1] D7~D5==000

D4(SFNM)D4=1 为特殊全嵌套方式,此时允许同级中断再次进入,一般用于多片级联方式;D4=0 为普通全嵌套方式,禁止同级中断再次进入。

D3(BUF)D3=1为缓冲工作方式,即8259通过总线驱动器和数据总线相连,此时SP#/EN#为输出,用于缓冲器选通信号;D3=0为非缓冲工作方式

D2(M/S)在缓冲方式下(BUF=1),表示本片为主片或从片:M/S# = 1为主片, M/S#=0为从片。

在非缓冲方式下,由SP#/EN#引脚设定主片和从片,本位不起作用

D1(AEOI)D1=1自动结束中断方式,在第二个INTA#时,清中断服务寄存器ISR中的对应位;D1=0 非自动结束中断方式,中断结束时发EOI命令清ISR中的对应位;

D0(mPM)D0=1为16位处理器体系;D0=0 为8085处理器体系;

eg. (默认D3=0,从片=>D2=0, EOI命令清ISR对应位D1=0)设ICW4,普通全嵌套=>D4=0,8088系统=>D0=1

1 | … |

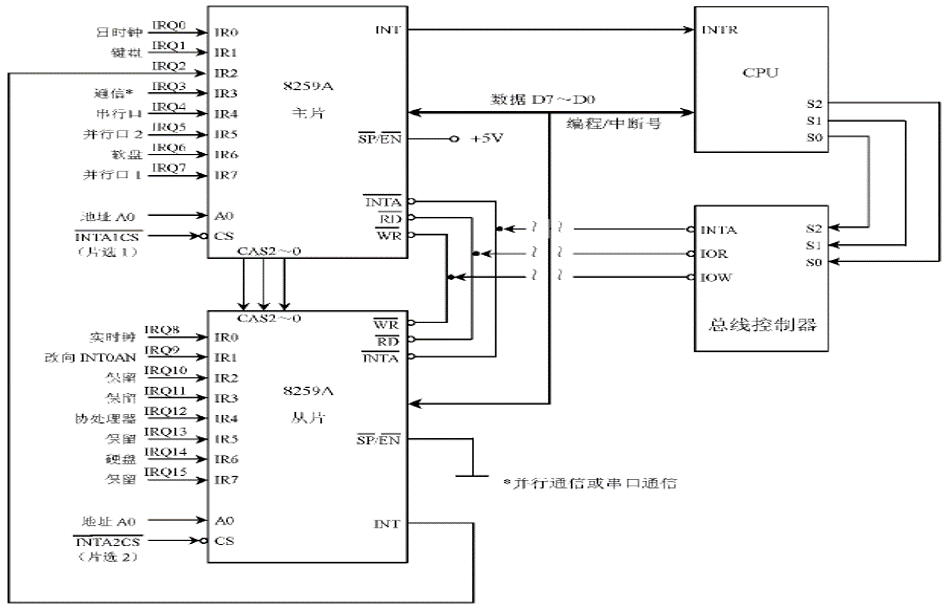

eg. 8259A以两片级联的方式管理15级向量中断。

1.两片级联时,CAS2~CAS0互联,从片的INT端输出作为主片第二级中断请求的输入。

2.端口地址,主片:020H~021H ,从片:0A0H~0A1H

3.主从片的中断请求信号为边沿触发

4.选择全嵌套方式,优先级排队顺序为0级最高。

5.主从片数据线采用非缓冲方式连接到CPU,主片SP#/EN#接+5V,从片SP#/EN#接地。

6.设定0~7级对应的中断号08~0FH,8~15级对应的中断号为70~77H。

1 | INTA00 EQU 20H ;8259A主片端口0 |

地址:

主片的端口地址在020H~03FH范围内,实际使用20H~21H两个端口。

从片的端口地址为0A0H~0BFH,实际使用0A0H~0A1H两个端口。

从片的INT信号与主片的IR2端相连,这样共构成15个向量中断。

主8259A的中断类型号08H~0FH;从8259A的中断类型号70H~7FH

操作命令

对8259的操作命令字设置靠A0和命令字特征位D4区分

8259A共有三个操作控制字:OCW1,OCW2和OCW3。

操作命令字可在任何时候写入8259A,且无顺序。

OCW1 [A0=1]

OCW1为中断屏蔽操作命令字;

A0=1 表示设置OCW1;

Mi=1 表示屏蔽IRi输入中断请求;

先读IMR,用逻辑或指令使对应屏蔽位置1(屏蔽该中断),用逻辑与指令使对应屏蔽位为0(开放该中断)。

1

2

3

4

5

6

7

8;若开放IR2的中断:

IN AL, 21H

AND AL, 11111011B

OUT 21H,AL

;若屏蔽IR2的中断:

IN AL, 21H

OR AL, 00000100B

OUT 21H,ALOCW2 [A0=0]

设置优先级循环方式和中断结束方式

1

2

3;非特殊的EOI命令为

MOV AL, 20H

OUT PORT, AL ;PORT为8259A的端口地址。OCW3 [A0=0]

A0=0,且D4D3=01,表示对OCW3编程

eg. 每片8259A只能管理8级中断,为了扩展系统的中断能力,

可把若干个8259A按级联方式连接起来。一般一个系统中最多级联8片8259A中断控制器,即中断级数可达64级。

- 级联方式

- 特殊完全嵌套方式

- 缓冲方式

1 | INTA1CS EQU 020H |

eg. 日时钟中断设置55ms定时,通过修改日时钟中断向量来对用户打字实现计时,

中断服务程序对中断次数进行统计,每18次后秒计数加1,然后逐一对分、时进行调整。

主程序功能对计时进行初始化为0,并清除错误计数缓存区,

等待键盘输入,判断键盘输入字符是否为命令,

若“ESC”则结束打字测试,若“回车”则显示输入一行字符所花时间以及键入字符错误个数,

此外均将键入字符与提示行字符进行逐一比较,以统计正确率

1 | TITLE TYPE_ER ---TEST TIME FOR TYPING EXERXISE |