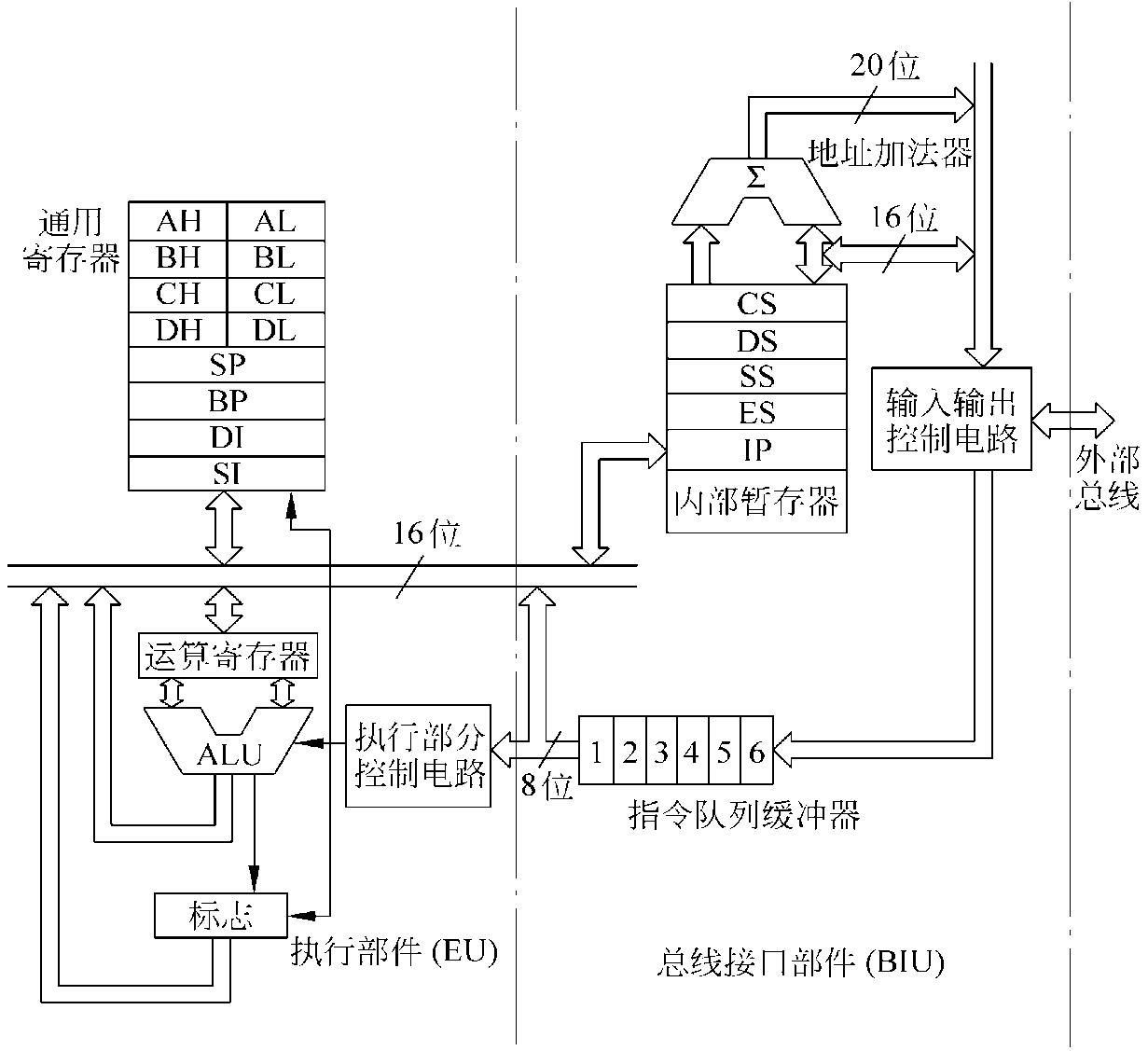

8086(微处理器CPU)组成

功能分类:

控制器, 运算器(ALU), 寄存器组, 系统总线

控制器分为:

- 指令寄存器IR (Instruction Register)

- 指令译码器ID (Instruction Decoder)

- 定时与控制电路

编程结构分类:(程序员和使用者的角度)

总线接口部件(bus interface unit, BIU)

传送data —> 存储器(Cache, RAM, ROM)、I/O端口(即输入输出接口电路)

16位段地址寄存器

CS (Code Segment) — 代码段寄存器

DS (Data Segment) — 数据段寄存器

SS (Stack Segment) — 堆栈段寄存器

ES (Extra Segment) — 扩展段寄存器

16位指令指针寄存器 IP (Instruction Pointer)

指向下一条指令的地址 in 当前代码段(CS)。取出一个字节指令后,IP += 1

转移指令、调用指令、中断和复位 ==> 改变IP值

20位物理地址的加法器

段地址*16+段内偏移量--20位实际物理地址

(CS, DS, SS, ES)*16 + (IP, SP, BP, DI, SI)

6个字节Bytes的指令队列(ISQ)

when 执行指令:

指令: 内存取 -> 指令队列缓冲器

输入输出控制电路

执行部件(execution unit, EU)

执行 指令

16位算术逻辑单元ALU

16位数据寄存器

AX、BX、CX、DX,又可以分为8个8位寄存器使用:

AH、AL、BH、BL、CH、CL、DH、DL

AX和AL可用作累加操作

BX可作基址指针寄存器,与DS配对

16位地址指针寄存器

SP (Stack Pointer)— 堆栈指针寄存器

堆栈段中的栈顶位置,与SS配对

BP (Base Pointer) — 基址指针寄存器

数据区的基址位置,与SS配对

SI (Source Index) — 源变址寄存器

某一存储单元的偏移地址,与DS配对

串操作:源string DS:SI

DI (Destination Index)— 目的变址寄存器

某一存储单元的偏移地址,与DS配对

串操作:目标string ES:DI

16位状态标志寄存器 FLAG

6个状态标志:

CF (Carry Flag)— 进(借)位标志,若运算结果最高位产生进位或借位则CF置“1”,否则置“0”;

AF (Auxiliary Flag)— 辅助进位标志,若低字节的第4位向上产生一个进位或借位,则AF置“1”,否则置“0”;

ZF(Zero Flag) — 零标志位, 若运算结果为零, 则ZF置1,否则置0;

SF(Sign Flag) — 符号标志位,若算数运算的结果为负,SF置1, 否则置0;

OF(Overflow Flag) — 溢出标志位,有符号数算术运算结果产生溢出, OF置“1”,否则置“0”;

PF(Pariy Flag) —奇偶标志位,逻辑运算中低8位所含1的个数为偶数则PF置“1” ,否则置“0”;

3个控制标志IF、DF、TF,余下7位保留:

DF(Direction Flag) —方向标志位

DF=1 串操作指令以递减顺序处理数据串;

DF=0 串操作指令以递增顺序处理数据串;

IF(Interrupt Flag) — 中断允许标志

IF=1 CPU允许接收外部可屏蔽中断请求,即开中断;

IF=0 关中断;

TF(Trace Flag) — 跟踪标志位 TF=1 处理器处于单步工作方式时,每执行完一条指令产生一个软件中断;

TF=0 正常工作;

- 编程结构(BIU && EU)工作过程:

when 两个字节Bytes为 empty in 指令队列 —->

CS:IP —-> 取指令(2 Bytes) in 存储器 —->

存放 指令队列

指令队列 —-> EU

译码分析 in EU控制电路

EU控制电路 send 控制信号 ——> 各个部件

各个部件执行

(special执行时)访问存储器 data -> 运算后结果存入存储器 :

EU get 操作数16位地址偏移量 —-> 20位物理地址 in BIU的地址加法器 —->

data in 存储器 —-> 内部EU数据总线 —-> ALU 计算结果 —->

20位实际目标地址(同上地址加法器产生) in 存储器

8086引脚信号

预备知识:

信号特点:引脚功能复用,不工作时8086 device处于高阻状态,总线时分复用

模式:最小模式(系统中只有一个8086微处理器),最大模式(系统中包含两个或多个微处理器)

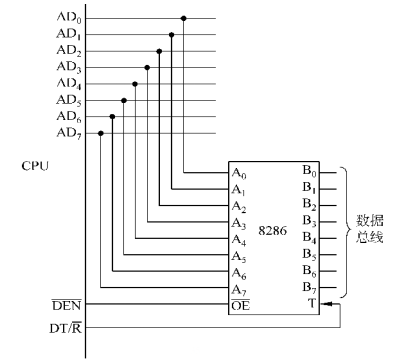

输入RESET == 1,处于复位状态时:

引脚功能:

在min最小模式下

AD15 ~ AD0 (地址/数据复用:双向工作)

- AD0: 可作为低8位数据的选通信号(when AD0 == 0)

A19/S6,A18/S5,A17/S4,A16/S3 (地址/状态复用:输出)

$\overline{BHE}$/S7 (高8位数据总线允许/状态复用:输出)

MN/$\overline{MX}$ (min/max 模式选择:输入)

$\overline{RD}$ (读信号:输出)

HOLD <=> $\overline{RQ}/\overline{GT0}$ (hold request 总线保持请求信号:输出)

HLDA <=> $\overline{RQ}/\overline{GT1}$ (hold acknowledge 总线保持应答信号:输出)

$\overline{WR}$ <=> $\overline{LOCK}$ (写信号:输出)

M/$\overline{IO}$ <=> $\overline{S2}$ (存储器/输入输出端口控制信号:输出)

DT/$\overline{R}$ <=> $\overline{S1}$ (data transmit/receive 数据收发信号:输出)

$\overline{DEN}$ <=> $\overline{S0}$ (data enable 数据允许信号:输出)

ALE <=> QS0 (address latch enable 地址锁存允许信号:输出)

$\overline{INTA}$ <=> QS1 (interrupt acknowledge 中断响应信号:输出)

NMI (non-maskable interrupt 非屏蔽中断输入:输入)

INTR (interrupt request 可屏蔽中断输入:输入)

$\overline{TEST}$ (测试信号输入:输入)

READY (准备好信号输入:输入)

RESET (复位:输入)

CLK (时钟信号输入:输入)

**在max最大模式下** :(协处理器:8087专用于数值运算,8089专用于输入输出控制)

$\overline{RQ}/\overline{GT0}$ (总线请求信号输入:输出)

$\overline{RQ}/\overline{GT1}$ (总线授权信号: 输出)

$\overline{LOCK}$ (总线封锁信号:输出)

$\overline{S2}\ \overline{S1}\ \overline{S0}$ (总线周期状态信号:输出)

QS0,QS1 (指令队列状态 IQS 信号:输出)

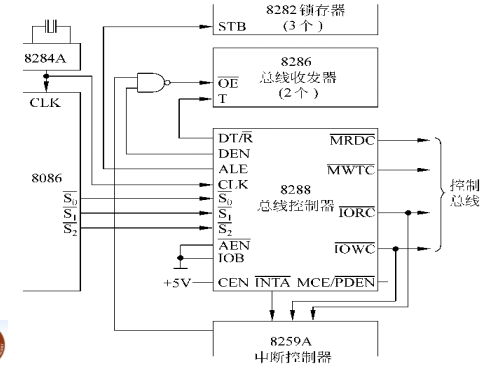

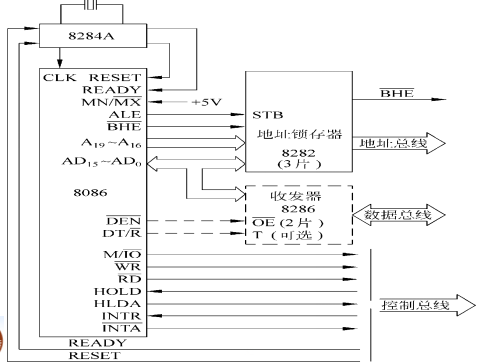

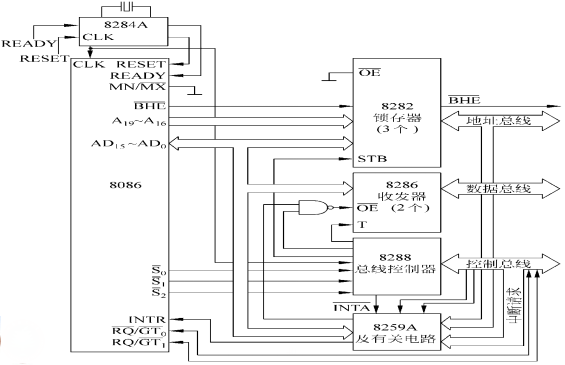

8086 与其他芯片连接(8284A,8282,8286,8259A,8288)

8284A 时钟发生器

输入:READY信号

RESET信号

输出:(发 => 8086的 CLK)

(发 => 8086的 READY)

(发 => 8086的 RESET)

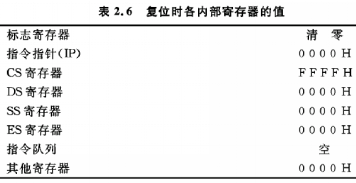

8282 地址锁存器

输入:STB (min模式:8086发出的ALE)

(max模式:8282发出的ALE)

$\overline{OE} == 0$

(8086发出的$\overline{BHE}$)

(8086发出的 A19 ~ A16,AD15 ~ AD0)

输出:$\overline{BHE}$

(发 => 地址总线)

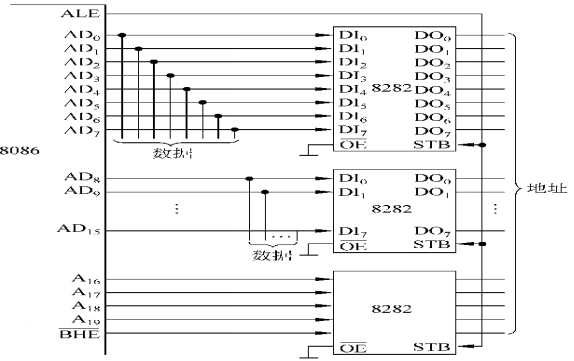

8286 数据收发器

输入:$\overline{OE}$(min模式:8086发出的$\overline{DEN}$ ),

(max模式:8288控制信号 DEN 和8259A发出的控制信号 与非)

T (min模式:8086发出的 DT/$\overline{R}$)

(max模式:8288发出的 DT/$\overline{R}$)

A7 ~ A0 (8086发出的AD7 ~ AD0)

输出:B7 ~ B0 (发 => 数据总线)

8259A 中断控制器 (max 模式下)

输入: (max模式:8288发出的$\overline{INTA}$)

(max模式:8288发出的$\overline{IORC}$)

(max模式:8288发出的$\overline{IOWC}$)

输出:(max模式:8259A发出控制信号) [和 8288控制信号 DEN 与非 => 8286 的 $\overline{OE}$]

(max 模式:发 => 8086的 INTR)

8288 总线控制器 (max 模式下)

功能:

主处理器和协处理器协调工作

总线的共享控制

对CPU发出控制信号变换和组合:

对存储器和 I/O 端口的读写信号

对地址锁存器 (8282) 控制信号

对数据收发器 (8286) 控制信号

对中断控制器 (8259A) 控制信号

输入:CLK (max模式:8284A 时钟发生器的输出)

$\overline{S0}\ \overline{S1}\ \overline{S2}$ (max模式:8288发出的$\overline{S0}\ \overline{S1}\ \overline{S2}$)

$\overline{AEN}$,IOB == 0

CEN == 5V

输出:ALE (max模式:发 => 8282 的STB)

DEN (max模式:和 8259A发出控制信号 与非,发 => 8286 的 $\overline{OE}$)

DT/$\overline{R}$ (max模式:发 => 8286 的 T)

$\overline{MRDC}$ (max模式:发 => 控制总线) (对存储器的读命令 memory read command)

$\overline{MWTC}$ (max 模式:发 => 控制总线) (对存储器的写命令 memory write command)

$\overline{IORC}$ (max模式:发 => 控制总线,8259A中断控制器) (对I/O的读命令)

$\overline{IOWC}$ (max模式:发 => 控制总线,8259A中断控制器) (对I/O的写命令)

$\overline{INTA}$ (max模式:发 => 8259A中断控制器) (中断响应信号)

总连接图

min 最小模式

max 最大模式

8086总线操作

周期

时钟周期:计算机主频决定的基本时间计量单位

指令周期:从取指令到执行指令完毕所需的时间

总线周期:外部存储器 or I/O端口 存or取 数据 的时间

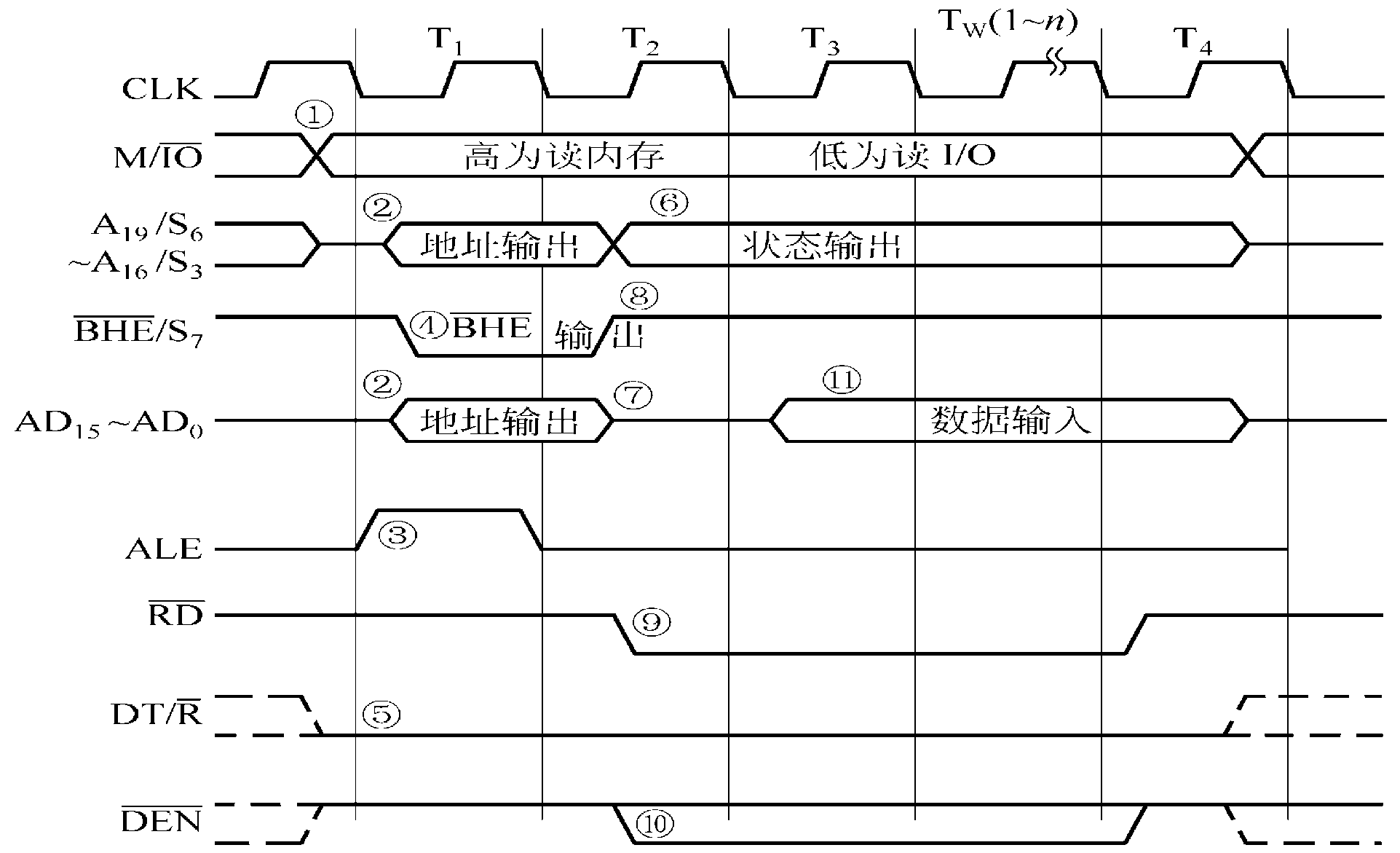

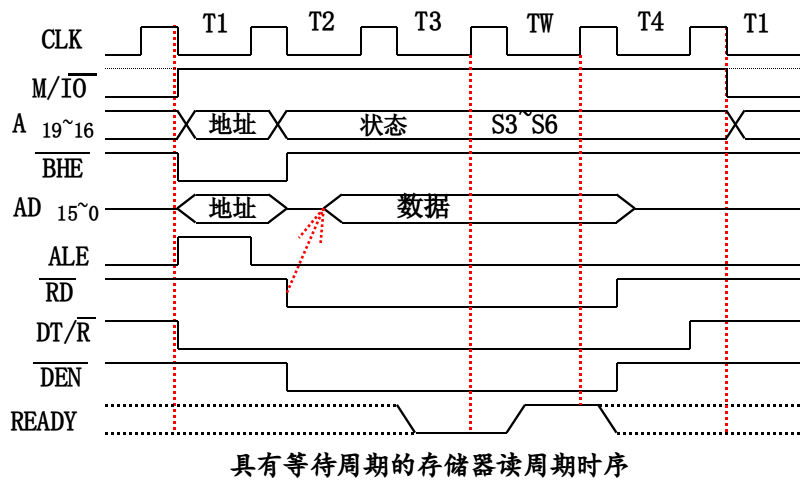

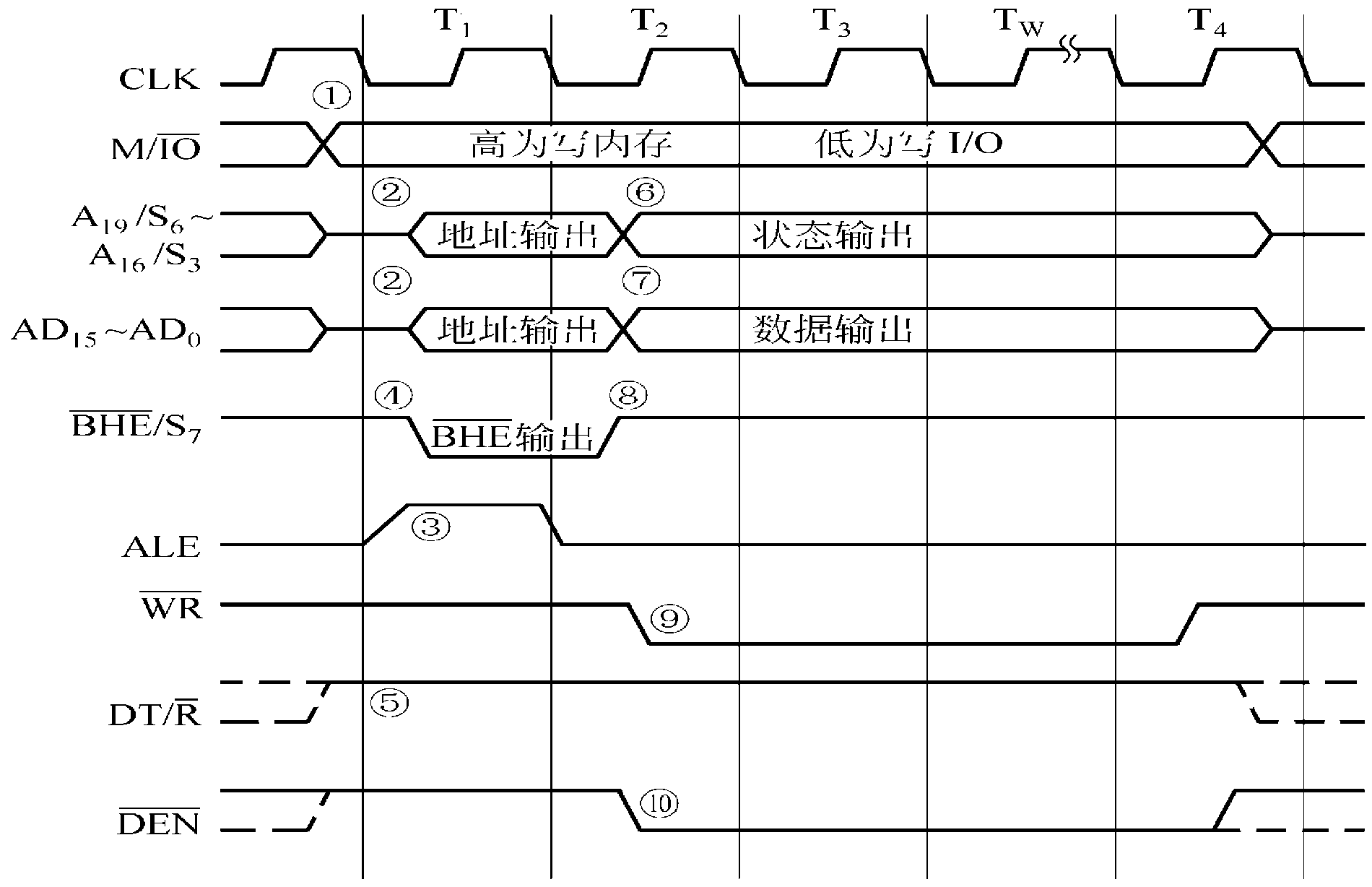

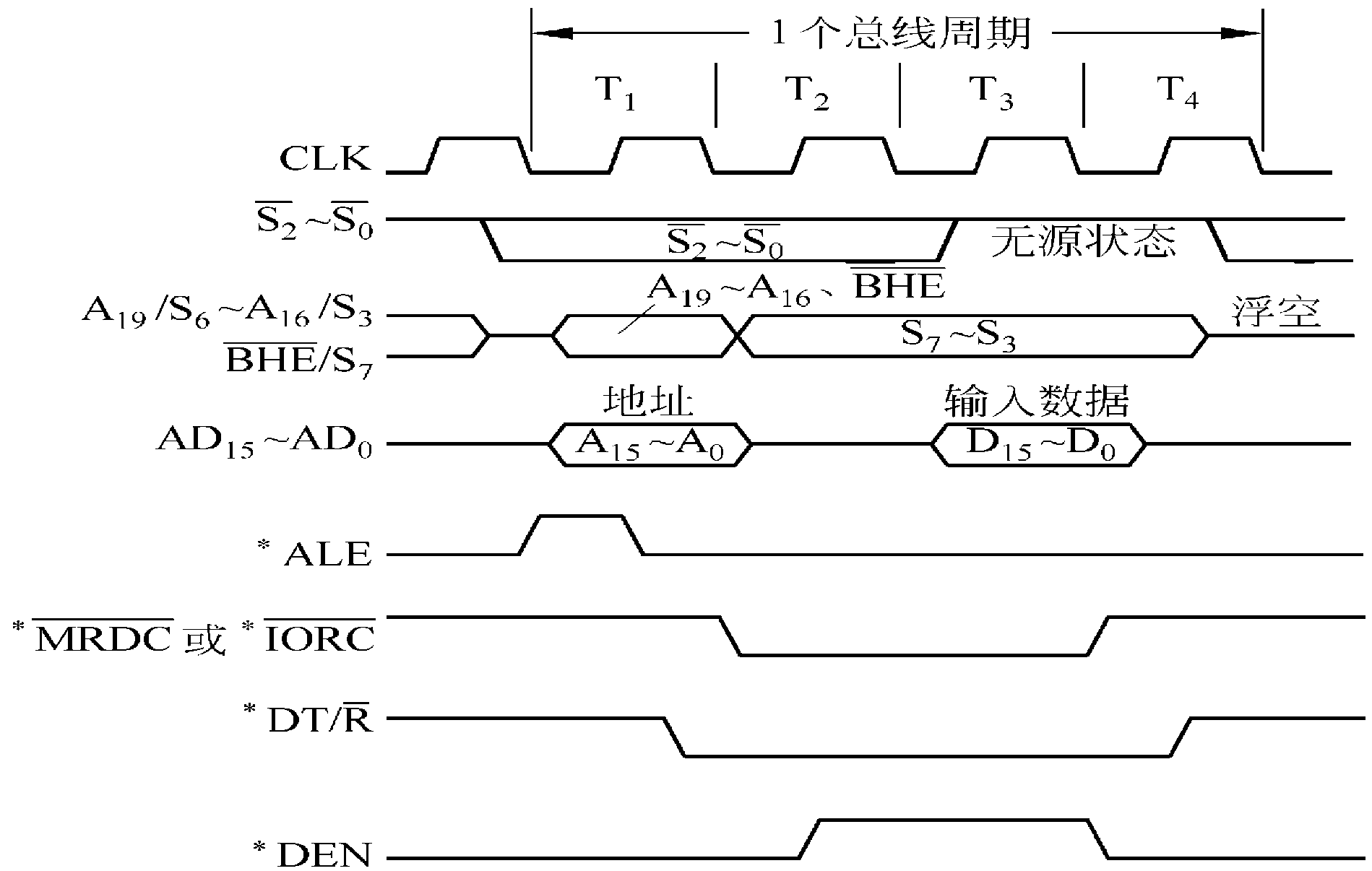

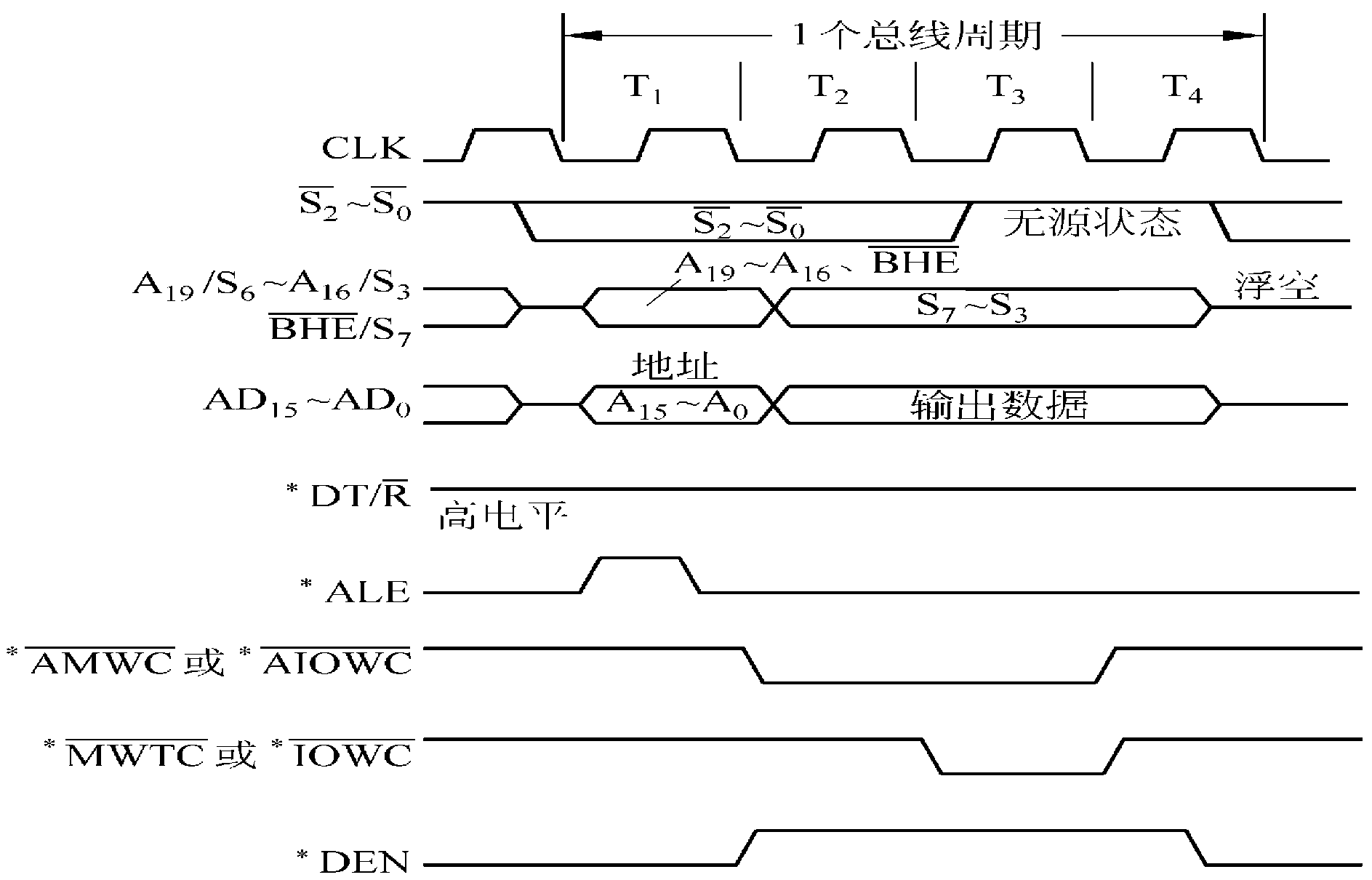

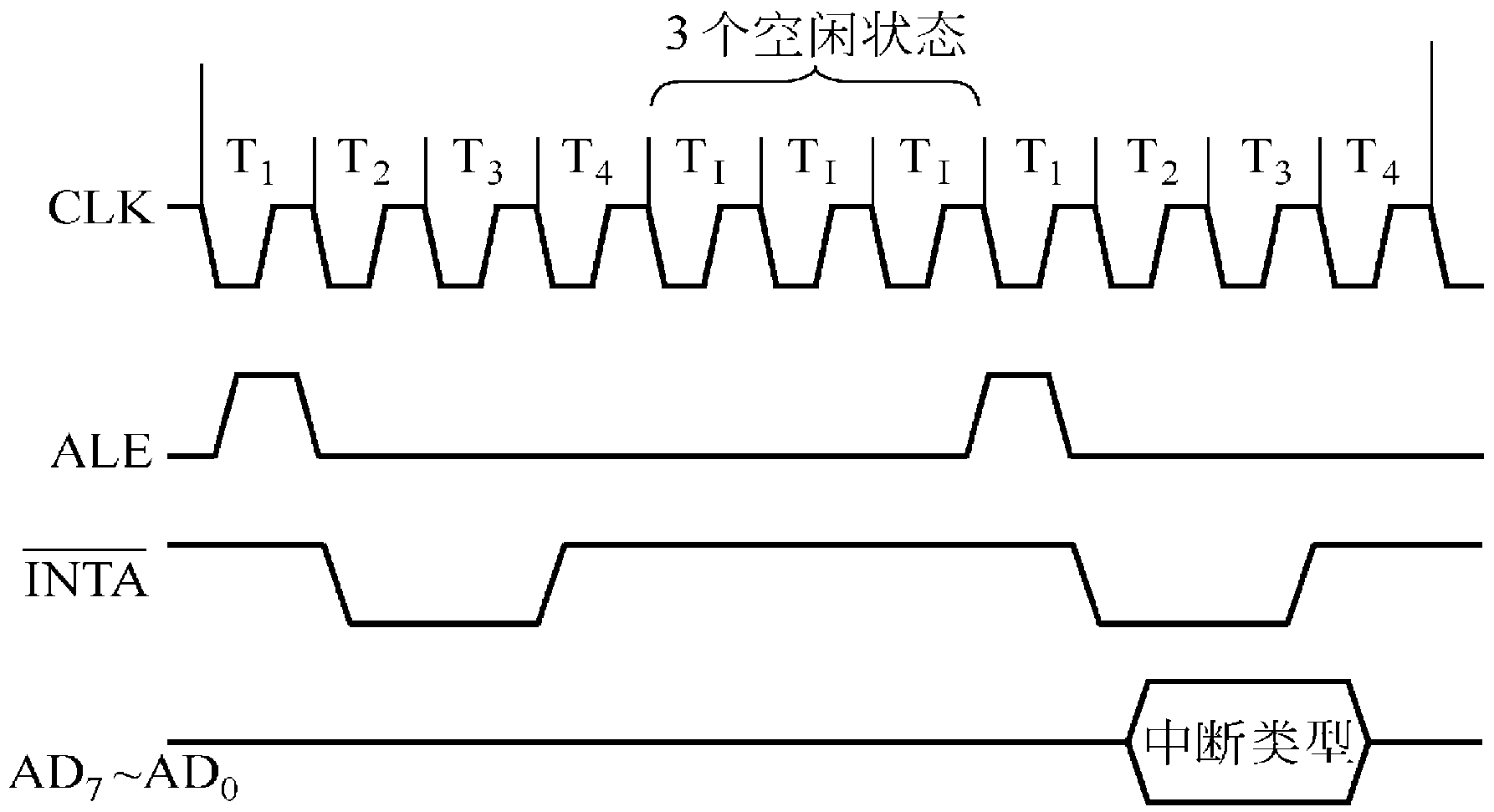

总线的4个状态:T1、T2、T3、T4;有时插入等待状态Tw,空闲状态Ti

T1:8086(AD15 ~ AD0,A19/S6 ~ A16/S3)发送 存储单元地址

T2:AD15 ~ AD0低16位成高阻状,A19/S6 ~ A16/S3 发送 总线周期状态

T3:AD15 ~ AD0 发送 data

Tw:插入n个附加的时钟周期Tw,直到外设或存储器完成数据传输 => READY == 1,进入T4

T4:总线周期结束

Ti:总线处于空闲

min && max 模式的 read && write

min read

T1:M/$\overline{IO}$ == 1 => memory输入输出,DT/$\overline{R}$ == 0 => data receive, ALE ==1 => address latch enable 地址锁存器enable , $\overline{BHE}/S7$ == 0 => A19/S6 ~ A16/S3不能状态复用,而是传address

T2: $\overline{BHE}/S7$ == 1 => A19/S6 ~ A16/S3状态复用,ALE ==0 => 无效化 地址锁存器,$\overline{RD}$ == 0 => 可read 数据,$\overline{DEN}$ == 0 => data enable 可传数据

T3:READY == 0 => 开始传数据

Tw:继续传数据,直到 READY == 1(CLK上升沿)时停止 =>进入T4

T4:结束,各信号归位

min write

max read

max write

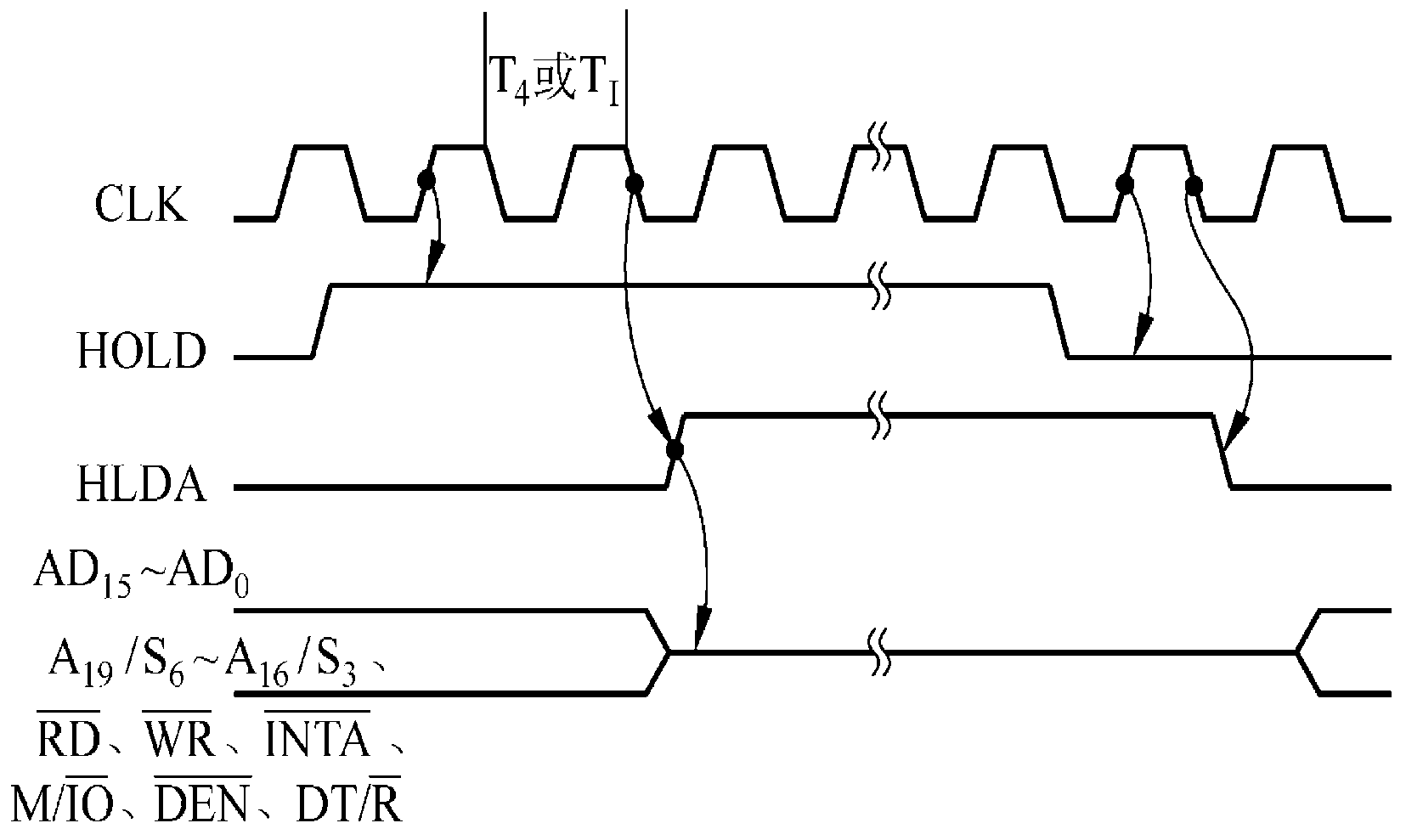

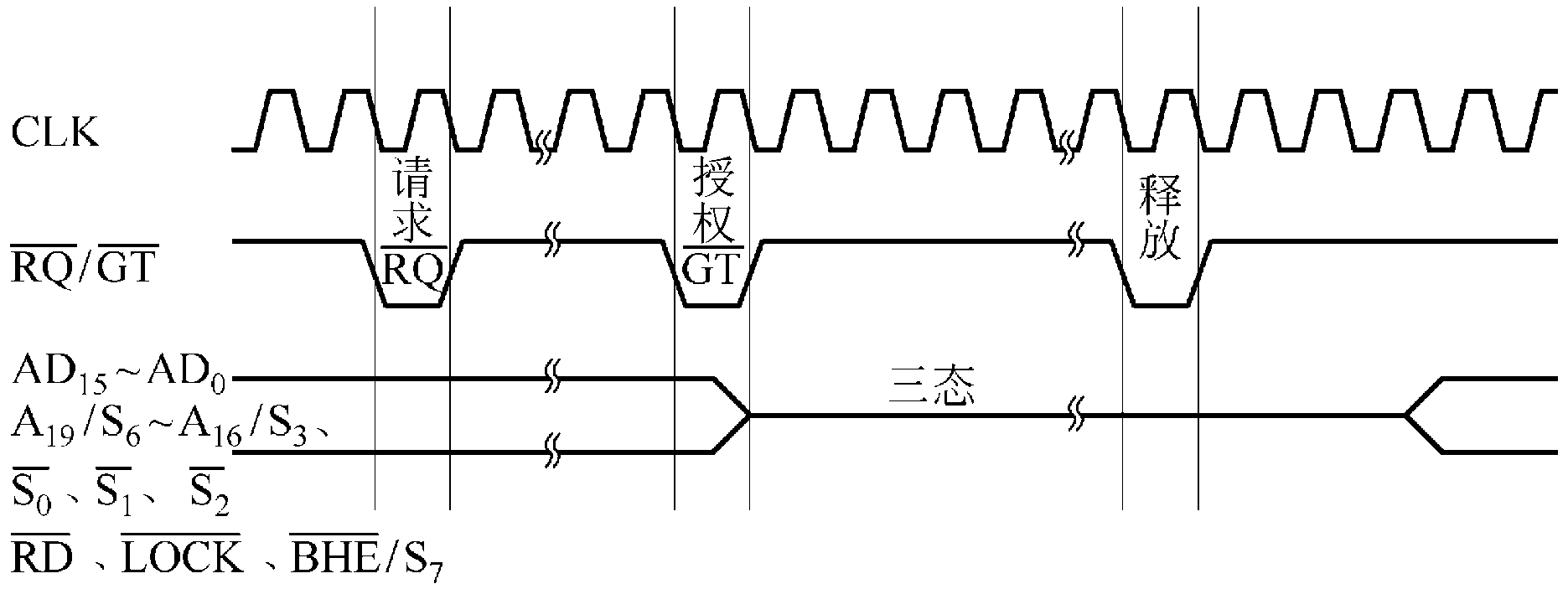

min && max 模式的总线 BUS

min 总线BUS保持

max 总线BUS请求,应答

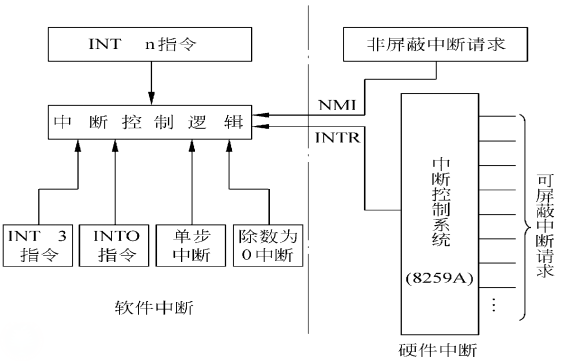

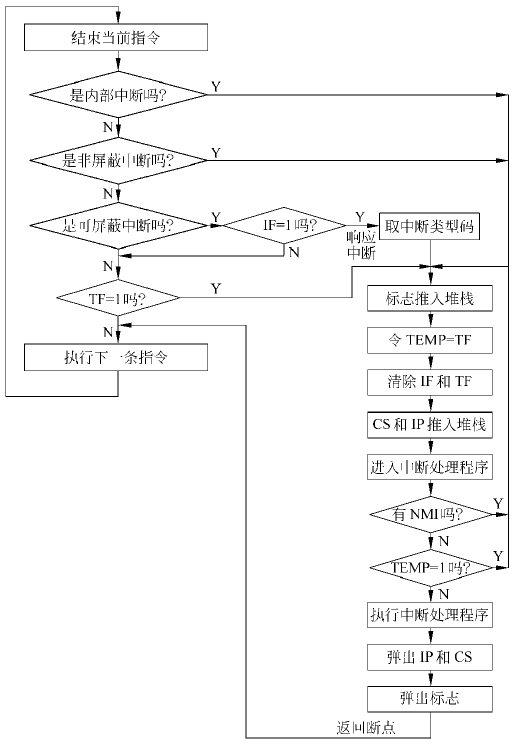

8086中断

中断类型:

硬件中断:由外部请求引起的中断

可屏蔽中断INTR

INTR高电平有效 (受IF控制),

CPU (每条指令的最后一个T状态) 检测INTR =>

CPU响应中断 => INTA有效 => 读取中断类型码 from 外设

非屏蔽中断NMI (INT 2)

NMI (上升沿有效) (不受CPU控制),

中断类型码为2(INT 2)

* 软件中断:由指令执行引起的中断

* DIV和IDIV指令(INT 0)

除数为0或商超过寄存器所能表达

* INT 指令 (INT n)

执行INT n指令引起的中断

* INTO 指令 (INT 4)

若OF=1,则指令INTO引起类型码为4的软件中断

* 单步中断 (INT 1)

若TF=1,则CPU每执行完一条指令后便产生类型码为1的软件中断

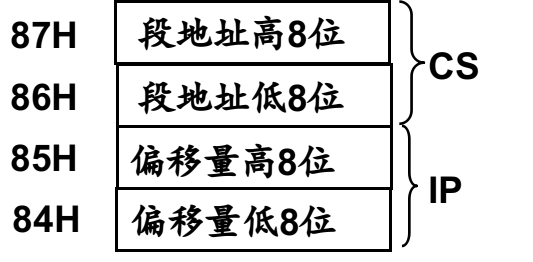

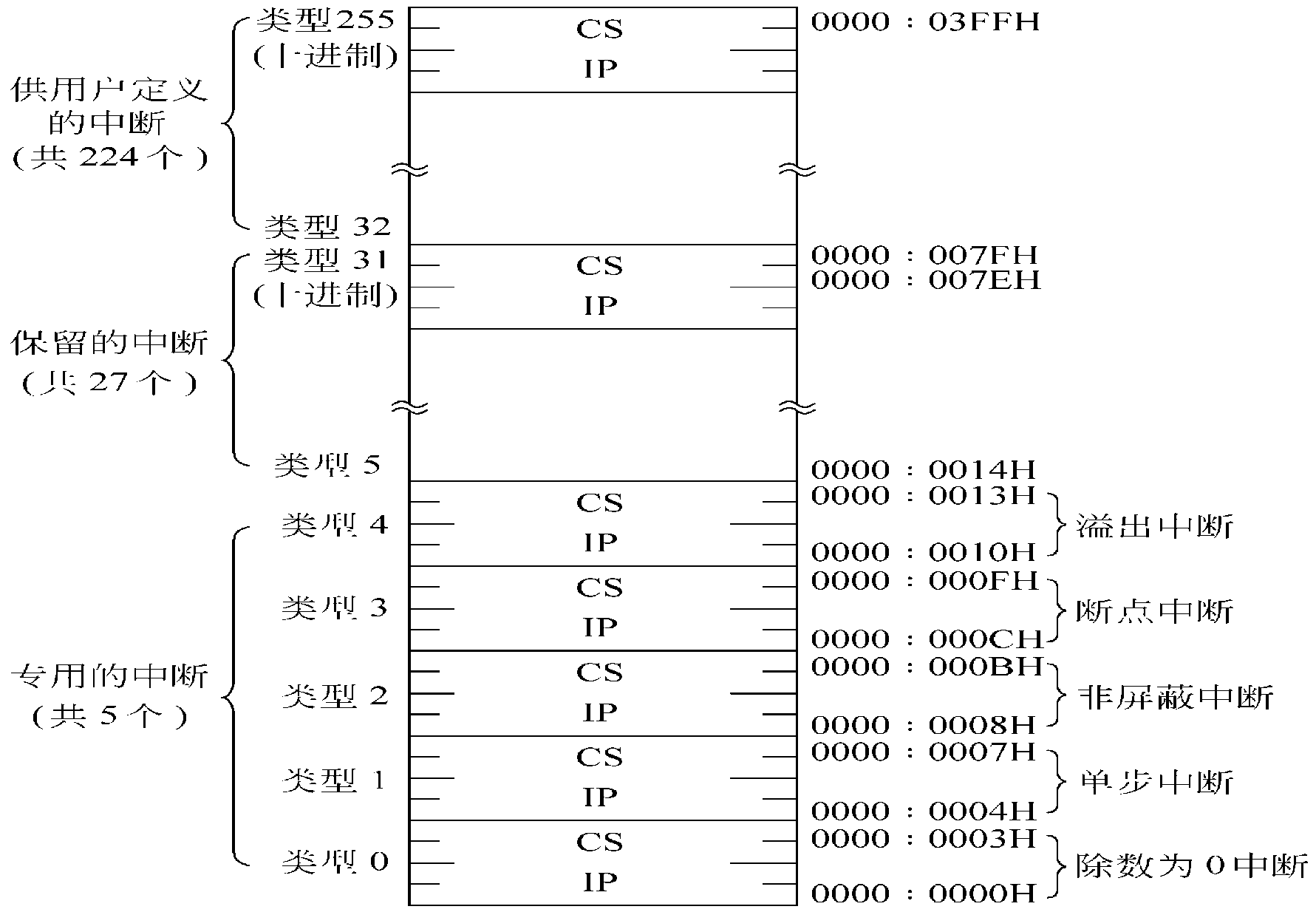

中断向量 (4 Bytes)

中断处理子程序的入口地址:

中断服务程序偏移地址IP(前 2 Bytes) + 中断服务程序段地址CS(后 2 Bytes)

eg: INT 21H => 21H * 4Bytes = 84H => 87H ~ 84H 作为 CS:IP

中断向量表

内存0段:0~3FFH = 4 bytes * 256 (0 ~ 0FFH 共 256 个中断向量)

0 ~ 4: 专用中断类型

5 ~ 1FH:保留中断类型 (可修改中断服务程序)[ 其中 8~0FH是8个硬件中断]

20H~0FFH:用户可用中断类型

中断响应

过程

软件中断 or NMI中断信号 or INTR中断信号( when CPU允许中断响应: IF=1)

==>进入中断响应周期: (4 种情况)

NMI中断信号 => 类型码是2

INTR中断信号(IF = 1) => 外设->低8位AD7 ~ AD0 传送中断类型码 ->CPU [占用两个总线周期]

- 第一周期用来通知发中断请求的设备,准备好中断类型码;

- 第二周期接收外设接口发来的中断类型码; (外设在第二个INTA负脉冲时,将中断类型码通过数据总线的低8位传给CPU)

- M/$\overline{IO}$ == 0,ALE 每个总线周期T1状态输出正脉冲,作为地址锁存信号。

中断指令 => 指令中类型码

程序出错产生中断 => 默认的类型码

==>FLAG 压入堆栈,set TF = 0,IF = 0,先压CS后压IP入堆栈

==>中断类型码 * 4 = 中断服务程序的入口地址

==>转入执行 中断服务程序

==>执行后,堆栈弹出 pop 恢复断点处 CS:IP 和 FLAG

==>返回执行下一条指令

- 注意:TF=1 处理器处于单步工作方式时,每执行完一条指令产生一个软件中断

8086和8088的区别

8086是16位数据总线,8088是8位数据总线

在处理16位数据字时:8088需要两步操作,而8086只需要一步

8086内部6字节指令缓冲队列,8088内部4字节指令缓冲队列

8086有M/$\overline{IO}$信号,8088对应为IO/$\overline{M}$