层次

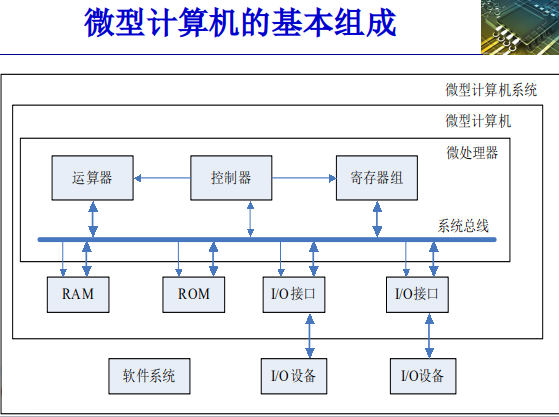

微处理器 (CPU):(8086, 80286)

控制器, 运算器(ALU), 寄存器组, 系统总线

控制器分为:

- 指令寄存器IR (Instruction Register)

- 指令译码器ID (Instruction Decoder)

- 定时与控制电路

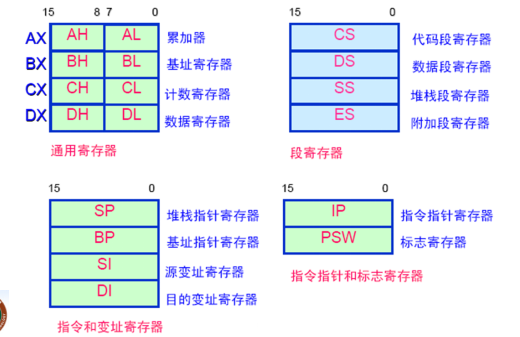

寄存器组分为:

- 累加器 AX

- 数据缓冲寄存器 DX

- 计数寄存器 CX

- 地址缓冲寄存器 BX

- 程序计数器 IP

- 状态标志寄存器 PSW

- 通用寄存器组 AX ~ DX

- 暂存器

系统总线(BUS)外部分为:

控制总线

一般为单向

地址总线

地址为n位宽,那么将有2^n个地址(即0~(2^n)-1),对应存储单元2^n Bytes

数据总线

双向传送

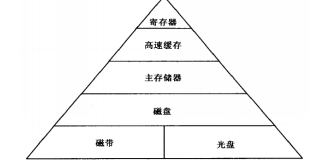

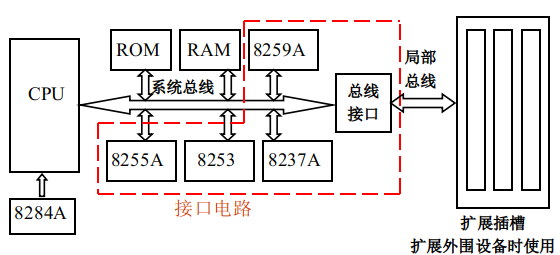

微型计算机 (增加Cache,主存储器:内存)

Cache RAM,RAM,ROM, I/O接口(即输入输出接口电路)

输入输出接口电路用芯片如:

- 缓冲器:74LS244、74LS245

- 锁存器:74LS373

- 可编程中断控制器8259A

- 可编程计数器/定时器8253

- 可编程并行/串行接口芯片8255A/8250A

- DMA控制器8237A模/数和数/模转换器

微型计算机系统 (MCS) (增加外存,外设)

I/O设备,软件系统

硬件结构

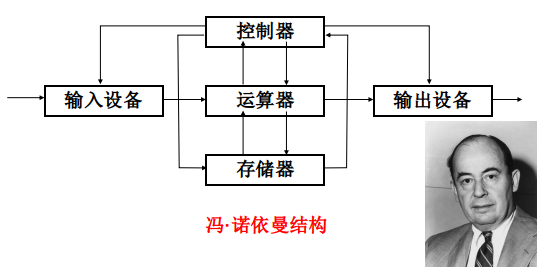

冯·诺依曼结构

地址码(2进制)-> data && program(2进制) 存放地址 [data && program不分开存]

程序计数器(PC)-> 指令序列(即程序)-> 控制器工作

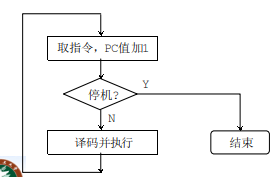

具体过程:

- 码段寄存器CS及指令指针寄存器IP -> 控制器 (取指)

- 控制器取 -> 指令代码 in 内存

- CPU中对代码 分析 (译码)

- 控制器send该指令功能对应控制信号 - > 各个部件

- 各个部件执行 (执行)

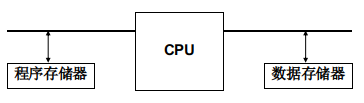

哈佛结构

- 存储器:程序存储器,数据存储器

- 总线分为:程序总线,数据总线

现代计算机

主存储器:冯·诺依曼结构

指令和数据合用

高速缓冲存储器(Cache):哈佛结构

指令Cache,数据Cache

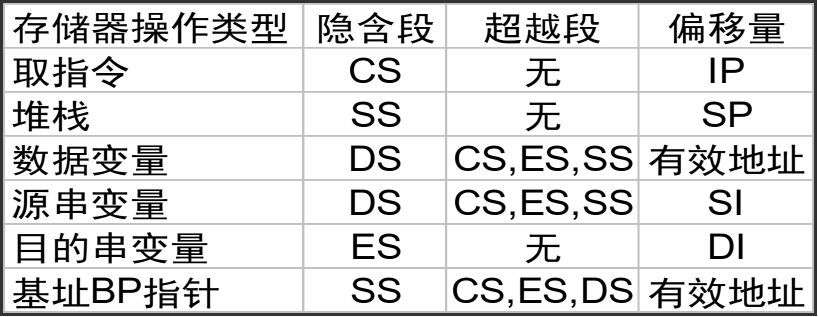

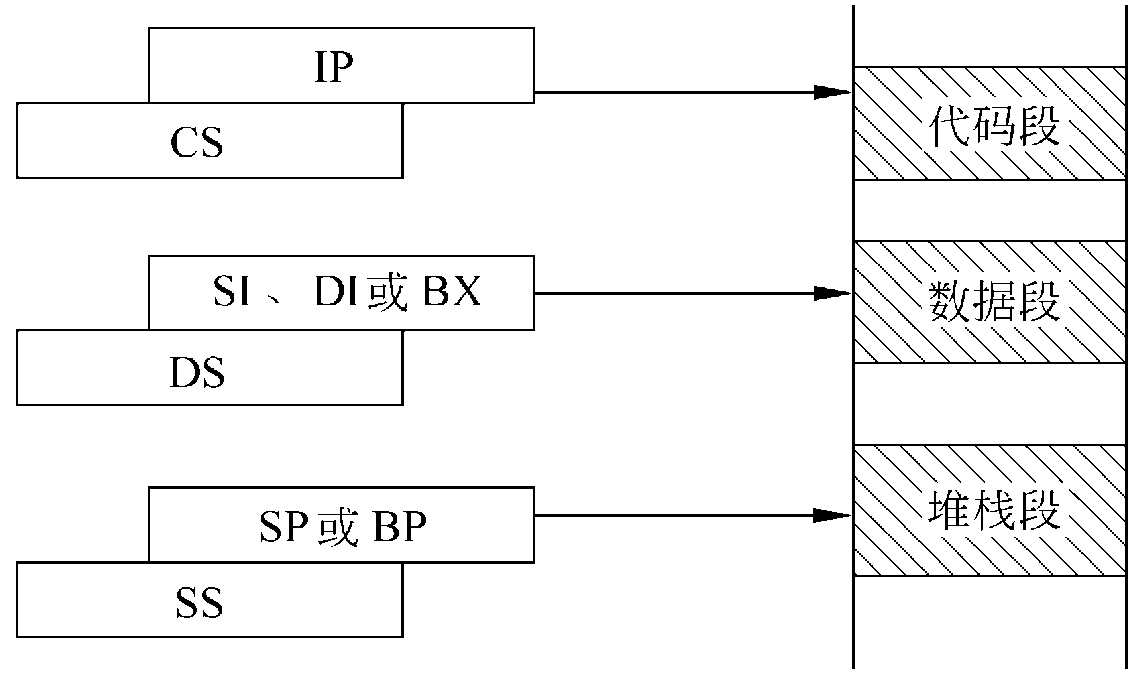

分段编址

分为代码段、数据段、堆栈段和附加段,一段最大 2^ 16 = 64KB

段地址分别由CS/DS/SS/ES四个寄存器给出

- 串操作:源串DS:SI ,目的串ES:DI

分段编址好处

- 大部分指令只涉及16位地址:在2 ^16 = 64kB的段内寻址 => 减小了指令长度、提高了执行速度

- 便于程序的浮动加载:程序本身是可浮动的,与物理地址(段地址无关),只与偏移地址有关

8086的固定用途存储区 [物理地址 20 bits]

00000H-003FFH,1KB 中断向量表;

B0000H-B0F9FH, 4KB 单色显示器显示缓冲区;

B8000H-BBF3FH,16KB 彩色显示器显示缓冲区;

FFFF0H-FFFFFH,16B 复位程序入口;

8086的I/O编址

端口:I/O接口电路中可被访问存储单元 (8086可以访问64KB的I/O端口)

I/O端口和存储器统一编址

可以用对存储器的指令来 => 对IO端口的访问

I/O端口单独编址

使用MOV指令访问存储器,M/$\overline{IO}$ = 1

使用IN/OUT指令访问端口,M/$\overline{IO}$ = 0

输入-IN, $\overline{RD}$=0

输出-OUT,$\overline{WR}$=0