微型计算机总线

总线概述

总线结构的优点:

便于采用模块化结构设计方法,简化系统设计;

便于开发相互兼容的硬件板卡和软件,标准总线得到各厂商的支持;

便于系统的扩充和升级,灵活性好;

便于故障诊断和维修

总线指标

总线宽度:指一次可以同时传输的数据位数

总线频率:指总线工作时每秒钟内能传输数据的次数

传输速率:指每秒钟能够传输的字节数 = 总线宽度 X 总线频率

eg. PCI总线的宽度为32位=4 B,总线频率为33MHz,所以,PCI的数据传输率为132MB/s(33*4)

总线功能分成

控制总线 [控制其他部件的部件称为总线主控 (master),被控部件称为从控(slave)]

地址总线 [地址总线是单向的,即地址信号只能由总线主控至从控。地址总线也是三态的]

数据总线 [数据总线是双向的。数据总线是三态的]

(数据总线的根数==总线的宽度)

总线的层次结构(内—>外)

片内总线:CPU或IO芯片内部,用于各功能部件之间

CPU总线:CPU、RAM、ROM、控制芯片组等芯片之间的信号连接[包括控制总线、地址总线和数据总线]

局部总线:主机板上的信息通道,连接主机板上各主要部件,通过扩展槽连接各种适配器

- ISA, EISA :(Extended) Industry Standard Architecture 16,32位标准总线,数据传输率16,33MB/s

- MCA : Micro Channel Architecture 32位标准总线,数据传输率40MB/s

- PCI : Peripheral Component Interconnect 32/64位标准总线,数据传输率132MB/s

- VESA : Video Electronic Standard Association 32位标准总线,数据传输率133MB/s

- AGP : Accelerated Graphics Port 是一种接口标准

系统总线:多处理器系统连接各CPU插件板的信息通道;系统机箱底板上;

外部总线:I/O设备(外设)与系统中其他部件(主机)间的公共通信通路

- SCSI-小型计算机系统互连;

- USB-通用串行总线

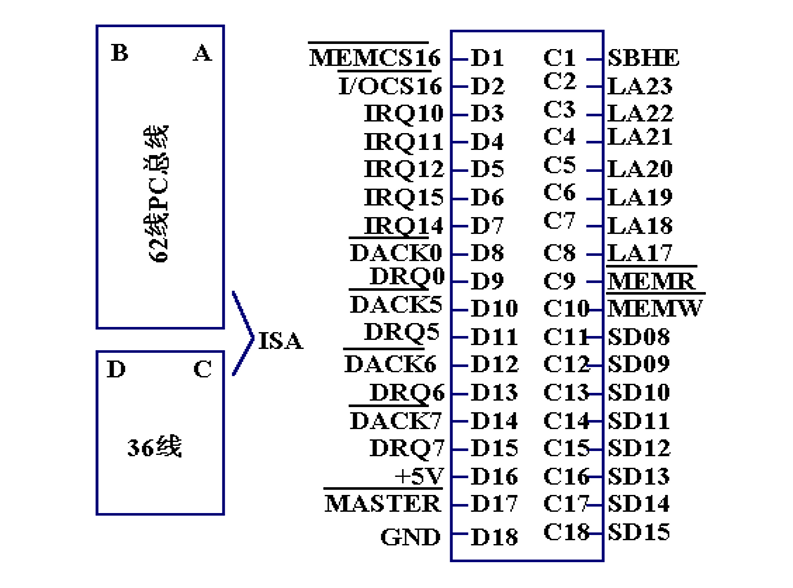

ISA总线

Industry Standard Architecture 16位标准总线,数据传输率16MB/s

数据线扩展为16位;

地址线扩展为24位,直接寻址2^24=16MB;

总线时钟为8MHZ,传输率8M*(16位/8bit)= 16MB/S

15个外部中断输入和7个DMA通道

62+36 =98 条信号线

SBHE:System Byte High Enable, when==1 数据总线SD8-SD15—->高位字节—->数据总线缓冲器

$\overline{MEM CS16}$:Memory 16 Bit Chip Select ==1 8位数据传输; ==0 16位数据传输

$\overline{I/O CS16}$:I/O 16-Bit Chip Select ==1 8位数据传输; ==0 16位数据传输

$\overline{MASTER}$[总线主模块信号] when扩展卡上有CPU或DMA控制器, ==0 获得总线控制权,并访问系统资源

OWS:Zero Wait State ==1 完成当前的总线周期,无插入Tw等待周期

$\overline{SMEMR}\ \overline{SMEMW}$ 对系统16MB存储器read,write[$\overline{MEMR}\ \overline{MEMW}$ 1MB范围内的存储器]

IRQ0-IRQ15:中断请求,主片的IRQ2—>从片(2片8259A)中断请求端INT

DRQ0、DRQ5-DRQ7:DMA请求,主片的DRQ0—>从片(2片主从式8237A)DMA 请求端

DACK0、DACK5-DACK7 :DMA应答信号

EISA总线

Extended Industry Standard Architecture 32位标准总线,数据传输率33MB/s

提高寻址能力(addr)、增加总线宽度(data)、增加控制信号 than ISA:

地址线为32条,直接寻址范围可达2^32=4GB

数据宽度为32位,自动进行8位、16位、32位数据转换

共有198条信号线,其中,98条是ISA原有的

时钟频率为8.3MHz,传输率为8.3MHz×32b/8b=33.2MB/s

PCI总线

Peripheral Component Interconnect 32/64位标准总线,数据传输率132MB/s

四个主要的标准规格:

分别支持32位与64位,其下又分成3.3V与5V两种信号

运行在33MHz或66MHz:数据传输率最大可达66M*(64位/8bit)=528MB/s

PCI总线特点

高传输率: PCI频率限于66MHz,最高传输率528MB/s

高效率: 集成高速缓冲器=>缓冲CPU数据, 支持突发数据传输模式

即插即用功能

系统和适配器两方面:

适配器中设EEPROM存按PCI规范的配置信息

PCI总线控制器测、调配置信息各参数,每PCI设备配256字节存放配置信息

独立于CPU

- 中间连接件机制:PCI控制器 && CPU 结构无关

- CPU不直接控制外设;

- 支持当前、未来CPU

负载能力强、易于扩展

- 负载能力比较强,而且PCI总线—>PCI控制器—>form多级PCI总线—>多个设备

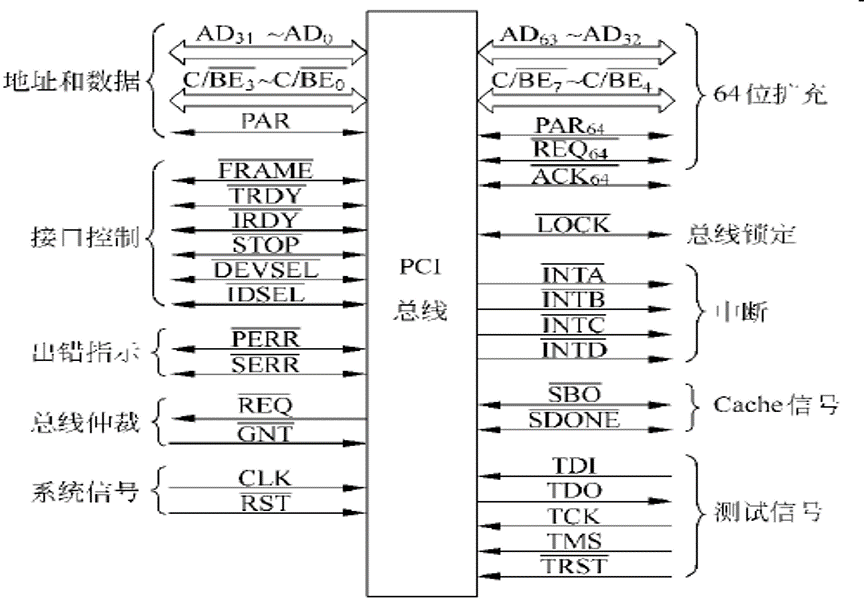

PCI 总线信号

1 系统信号

CLK:总线时钟输入信号0HZ~66MHz,除$\overline{RST}$,$\overline{INTA~D}$外,余信号在CLK 上升沿同步

$\overline{RST}$: PCI 专用寄存器、定时器相关的信号恢复到规定的初始状态

2 地址和数据信号

AD[31:00]地址/数据复用信号:双向(输入/输出)三态信号

$C/\overline{BE[3:0]}$总线命令&&字节使能信号:地址期,定义总线命令;数据期,作字节使能

总线命令的作用

规定主从设备之间传输信息的类型

0000 中断确认 中断识别命令

0001 特殊周期 提供在PCI上的简单广播机制

0010 I/O读 从I/O口地址中读数据

0011 I/O写 向I/O地址空间写数据

0110 存储器读 从内存空间中读出数据

0111 存储器写 向内存空间写入数据

1100 多重存储器读 只要$\overline{FRAME}$==0,保持存取管道连续,以大量传输数据

PAR奇偶校验信号: 进行偶校验AD[31:00]、$C/\overline{BE[3:0]}$双向

3 接口控制信号

$\overline{FRAME}$:帧同步信号,由启动方驱动,==0 数据帧访问开始&& 数据传输keep

$\overline{IRDY}$: (Initiator Ready):启动方准备好信号

$\overline{TRDY}$:(Target Ready)目标方准备好信号

$\overline{STOP}$:停止数据传送信号,从设备要求主设备

$\overline{LOCK}$: 总线锁定信号, ==0时阻其他设备 中断当前的总线周期

IDSEL: 初始化设备选择信号

$\overline{DEVSEL}$: 设备选择信号,此信号==0时,通知主设备,从设备被选中

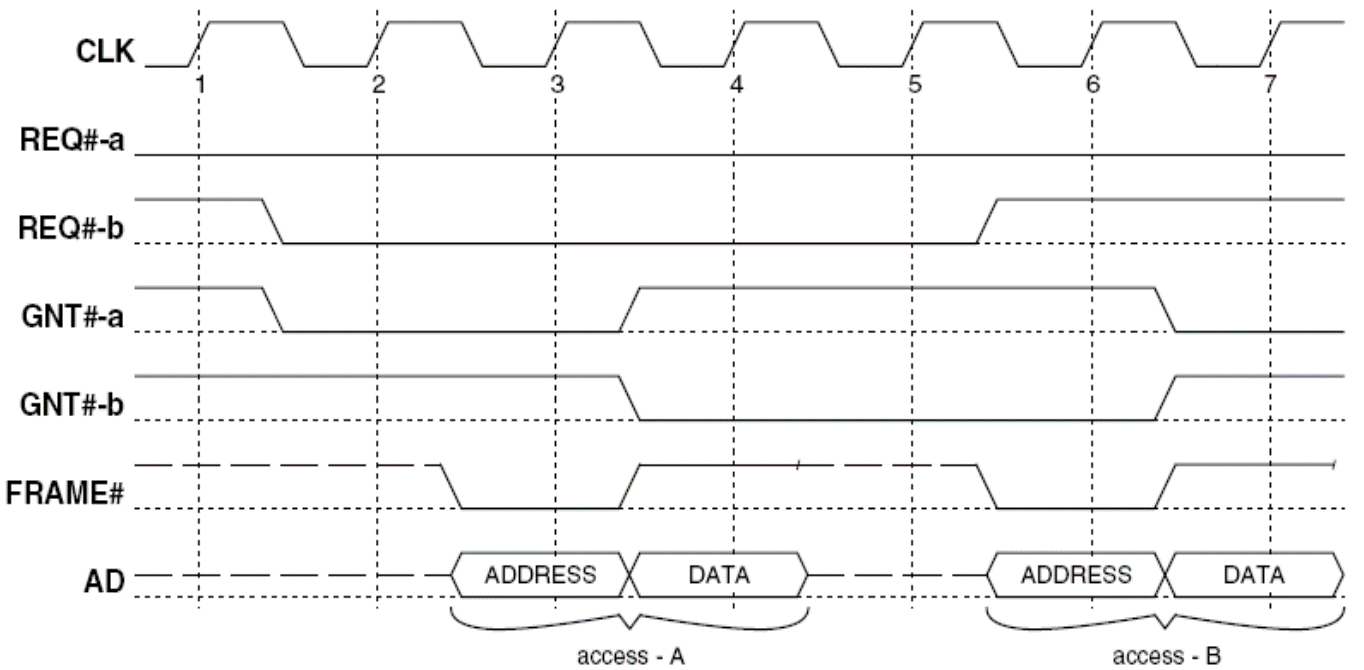

4 总线仲裁信号

$\overline{REQ}$: 总线请求信号,==0 表示驱动它的设备要求使用总线

$\overline{GNT}$: 总线允许信号,==0仲裁器同意(请求总线的设备)使用总线

PCI使用同步集中式隐含仲裁。

- 对于每个主设备都有唯一的请求($\overline{REQ}$)和允许信号($\overline{GNT}$)连接到仲裁器,利用请求-允许方式完成总线的切换,仲裁过程在上一次访问期间隐性完成。

仲裁器可以使用先来先服务法、循环轮流法和其他一些优先权排列法

eg. 设备B的优先级高于设备A。

PCI主设备必对它要执行每次传输 请求总线仲裁

5 错误报告信号

$\overline{PERR}$: 数据奇偶校验parity错误报告信号

$\overline{SERR}$: 系统错误报告信号, PCI的任一设备来驱动

6 中断信号

$\overline{INTA-D}$: 四条中断请求线, 单功能设备只能用$\overline{INTA}$,后三个信号用于多功能设备

7 Cache 支持信号

$\overline{SBO}$: PCI Cache /bridge的输出信号, PCI总线上高速缓冲存储器子系统的输入信号

$\overline{SDONE}$: 侦听完成信号。是PCI Cache / bridge 输出信号,在PCI总线上高速缓冲存储器子系统的输入信

8 64位总线扩展信号

AD[63:32] : 扩展的32位地址和数据多路复用线

$C/\overline{BE[7:4]}$: 总线命令&&字节使能多路复用信号

$\overline{REQ64}$: 64位传输请求, 本设备要求采用64位传送数据

$\overline{ACK64}$: 64位传输确认信号,表示目标方同意执行64位传输

PAR64: 奇偶校验信号,是AD[64:32]和C/BE[7:4]的校验位

9 边界扫描信号JTAG

TCK:边界扫描的测试时钟,用于记录状态信息,测试设备的输入输出数据

TDI: 测试输入信号,通过串行移位将测试数据和指令送入设备中

TDO: 测试输出信号,串行移位设备中的输出数据和指令

TMS: 测试模式选择,用于初始化“测试访问口控制器”的状态

$\overline{TEST}$: 测试复位,用于初始化“测试访问口控制器”

PCI 数据传输

由一个地址期和一个或多个数据期所组成

[地址期为一个时钟周期,数据期可插入Tw,等待由于主or从设备未准备好造成]

事件在时钟下降沿同步, 在每个时钟周期中间部位发生

总线设备在总线周期开始的上升沿, 采样总线上的各信号

信号变化在时钟下降沿 + 信号采样在时钟上升沿

传输过程: 主设备->$\overline{FRAME}$==0开始; $\overline{FRAME}$==1后最后一个数据传输

PCI编码

I/O空间:位于主机系统

正向译码:

负向译码:其他设备未被选中时,由总线扩展桥发$\overline{DEVSEL}$来响应

内存空间:位于主机系统

配置空间:分布于各个设备中

基本配置空间为256字节。

头标区(0~3FH)64字节,描述与系统相关的信息

设备相关区(40H~FFH)192字节,描述设备本身功能细节

配置寄存器如下

三种头标类型[头标区(0~3FH)] (前16字节(0~0FH)定义是统一的,后48字节的定义不同)

2类:专用于PCI-CardBus桥

1类:专用于PCI-CPI桥

0类:适用于普通的PCI设备和CPI扩展桥

10H~27H共16+8=24个字节,组成:

6个32位(4B)寄存器,可申请6个32位寻址存储区,or

3个64位(8B)寄存器,可申请3个64位寻址存储区,or

6个32位(4B)寄存器,可申请6个32位寻址IO端口;

基于映射机制:基址寄存器第0位决定

0-存储器空间; 1-IO空间

基址寄存器第1、2位==>存储空间基址寄存器长度32 or 64位&&存储空间大小

提供设备的各种寄存器地址(映射到统一的空间,用来支持即插即用功能)、设备及其类型、设备运行时需要存储空间和IO接口

设备所需存储器和IO端口统一编址,使互不冲突

为需要的设备分配中断类型号

外部总线

RS232;

IDE(IntegratedDrive Electronics):原指把控制器和盘体集中在一起的硬盘驱动器,主要用于主机和硬盘、光驱、软驱之间的连接

[ATA(Advanced Technology Attachment):IDE技术规范归纳成为全球硬盘标准]

SATA(SerialATA):SATA规范将硬盘的外部传输速率理论值提高到了150MB/s,比标准ATA/100高出50%。

SCSI(SmallComputer System Interface):用于小型机、工作站、服务器或其他多任务、高性能、智能外设。

USB:通用串行总线